Макетная плата для оценки ошибок ПЛИС JTAG Open3S500E, стандарт # XC3S500E Spartan-3E, XILINX ПЛИС + комплект ядра XC3S500E

Development Board Store - Надежность 97.5%

Более 1496 подписчиков, дата открытия магазина 18.02.2013

- Положительные оценки: 98% (85)

- Соответствие описанию: 98%

- Отвечает на сообщения: 98%

- Скорость отправки: 96%

Последнее обновление: 19.03.2022

FPGA JTAG Open3S500E стандарт # XC3S500E Spartan-3E XILINX FPGA оценочная макетная плата + XC3S500E Core Kit

Обзор

Обзор

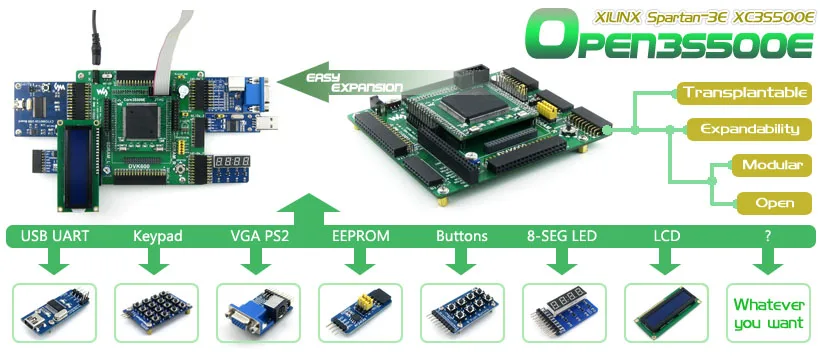

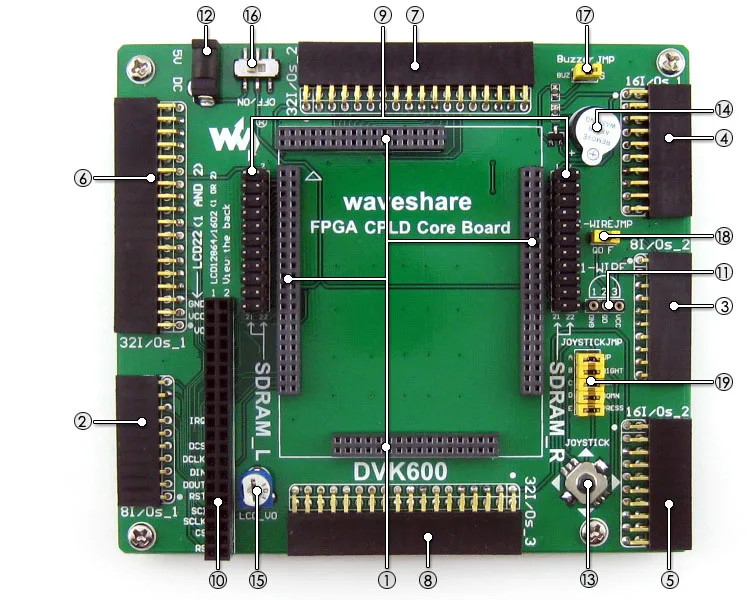

Open3S500EЯвляется макетной платой FPGA, которая состоит из материнской платыDVK600И основная плата FPGACore3S500E.

Open3S500E поддерживает дальнейшее расширение с различными дополнительными досками аксессуаров для конкретного применения. Модульная и открытая конструкция делает его идеальным для начала разработки приложений с устройствами ПЛИС серии XILINX Spartan-3E.

Что на материнской плате Разъем основной платы FPGA CPLD:Для легкого подключения основных плат, которые объединяют встроенный чип FPGA CPLD

Интерфейс 8I/Os_1,Для подключения досок/модулей

Интерфейс 8I/Os_2,Для подключения досок/модулей

Интерфейс 16I/Os_1,Для подключения досок/модулей

Интерфейс 16I/Os_2,Для подключения досок/модулей

Интерфейс 32I/Os_1,Для подключения досок/модулей

Интерфейс 32I/Os_2,Для подключения досок/модулей

Интерфейс 32I/Os_3,Для подключения досок/модулей

Разъем основной платы FPGA CPLD:Для легкого подключения основных плат, которые объединяют встроенный чип FPGA CPLD

Интерфейс 8I/Os_1,Для подключения досок/модулей

Интерфейс 8I/Os_2,Для подключения досок/модулей

Интерфейс 16I/Os_1,Для подключения досок/модулей

Интерфейс 16I/Os_2,Для подключения досок/модулей

Интерфейс 32I/Os_1,Для подключения досок/модулей

Интерфейс 32I/Os_2,Для подключения досок/модулей

Интерфейс 32I/Os_3,Для подключения досок/модулей

Все вышеуказанные интерфейсы ввода-вывода:

Возможность имитации как USART, I2C, SPI, PS/2 и т. д. Возможность управления устройствами, такими как FRAM, FLASH, USB, Ethernet и т. д.Для джемперов 17-19:

Короткая перемычка для подключения к I/Os, используемой в примере кода Откройте перемычку, чтобы подключиться к другим пользовательским контактам через перемычкиDVK600 поддерживает широкий спектр различных материнских плат, поэтому некоторые интерфейсы могут быть не подключены и бесполезны при подключении к определенной материнской плате. Например, при подключении к Core3S500E/CoreEP2C8, 32I/Os_3 'не подключен.

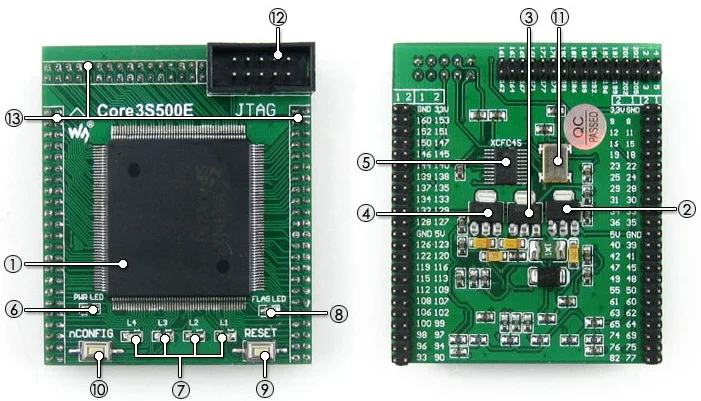

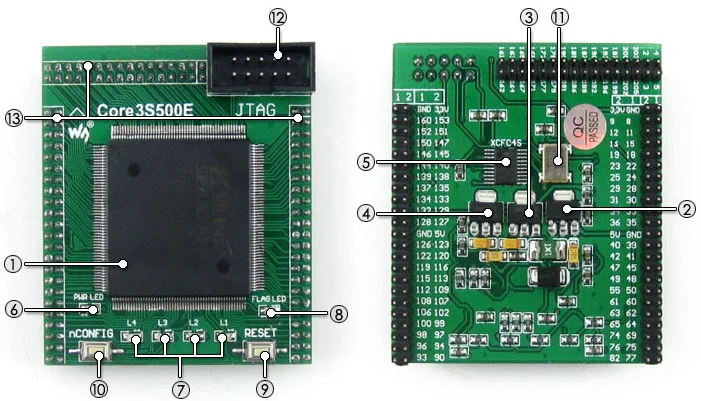

Что на Core3S500E XC3S500E:Устройство плис XILINX Spartan-3E, которое имеет:

Рабочая частота:50 МГц

Рабочее напряжение:1,15 в ~ 3,3 В

Посылка:QFP208

I/Os:116

LEs:500K

RAM:360 КБ

DCMs:4

Отладка/программирование:Поддержка jtag

AMS1117-3.3,Регулятор напряжения 3,3 В

AMS1117-2.5,Регулятор напряжения 2,5 в

AMS1117-1.2,Регулятор напряжения 1,2 в

XCF04S,Встроенная последовательная флэш-память для хранения кода

Индикатор питания

Светодиоды

Индикатор инициализации FPGA

Кнопка сброса

Кнопка nCONFIG:Для повторной настройки чипа FPGA эквивалент перезагрузки питания

Активный кварцевый генератор 50 м

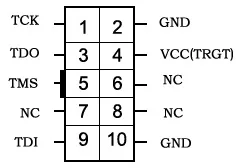

Интерфейс JTAG:Для отладки/программирования

Расширитель контактов FPGA,VCC, GND и все порты ввода-вывода доступны на разъемах расширения для дальнейшего расширения

Фотографии

XC3S500E:Устройство плис XILINX Spartan-3E, которое имеет:

Рабочая частота:50 МГц

Рабочее напряжение:1,15 в ~ 3,3 В

Посылка:QFP208

I/Os:116

LEs:500K

RAM:360 КБ

DCMs:4

Отладка/программирование:Поддержка jtag

AMS1117-3.3,Регулятор напряжения 3,3 В

AMS1117-2.5,Регулятор напряжения 2,5 в

AMS1117-1.2,Регулятор напряжения 1,2 в

XCF04S,Встроенная последовательная флэш-память для хранения кода

Индикатор питания

Светодиоды

Индикатор инициализации FPGA

Кнопка сброса

Кнопка nCONFIG:Для повторной настройки чипа FPGA эквивалент перезагрузки питания

Активный кварцевый генератор 50 м

Интерфейс JTAG:Для отладки/программирования

Расширитель контактов FPGA,VCC, GND и все порты ввода-вывода доступны на разъемах расширения для дальнейшего расширения

Фотографии

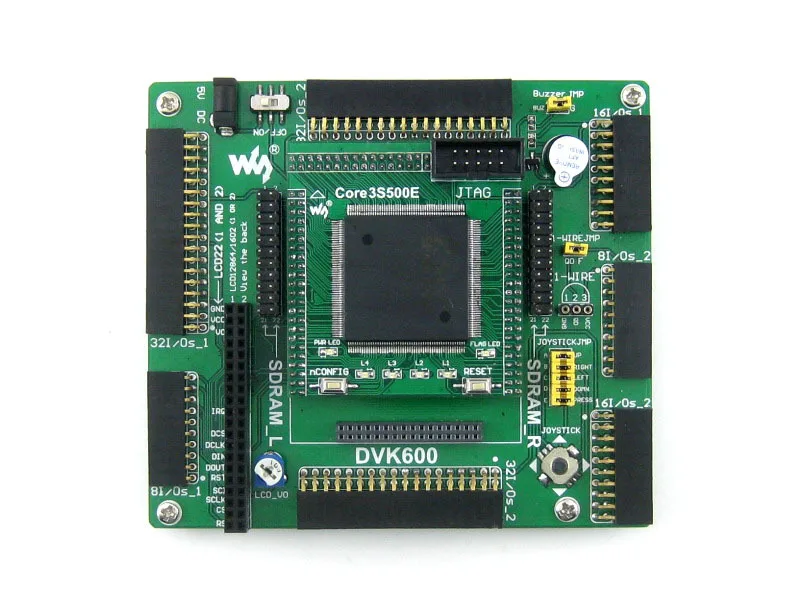

Макетная плата Open3S500E

Макетная плата Open3S500E

Макетная плата Open3S500E

Макетная плата Open3S500E

Макетная плата Open3S500E вид сзади

Макетная плата Open3S500E вид сзади

Материнская плата DVK600

Материнская плата DVK600

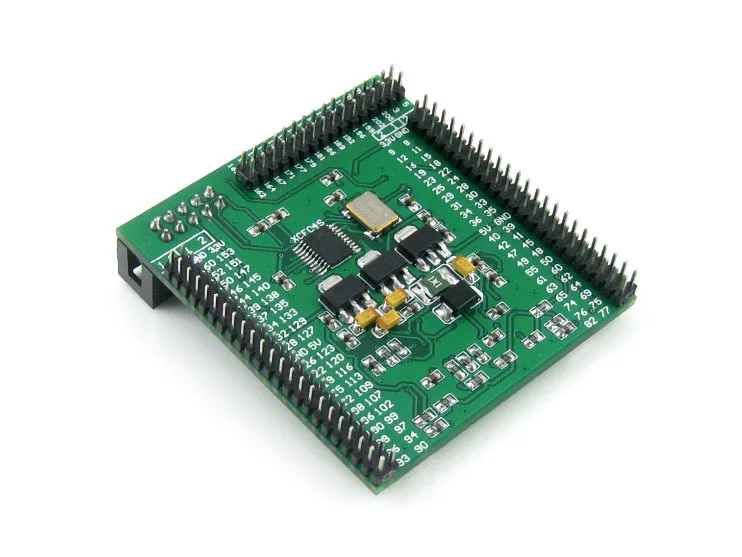

Основная плата FPGA Core3S500E

Основная плата FPGA Core3S500E

Основная плата FPGA Core3S500E

Основная плата FPGA Core3S500E

Подключение к различным периферийным устройствам

Подключение к различным периферийным устройствам

Подключение к LCD12864

Подключение к LCD12864

Подключение к LCD1602

Подключение к LCD1602

Подключение к плате RS232

Подключение к плате RS232

Подключение к USB-плате UART

Подключение к USB-плате UART

Подключение к светодиодной плате 8 SEG

Подключение к светодиодной плате 8 SEG

Подключение к 8 кнопкам

Подключение к 8 кнопкам

Подключение к 4x4 клавиатуре

Подключение к 4x4 клавиатуре

Подключение к плата EEPROM

Подключение к плата EEPROM

Несколько периферийных устройств, подключенных к одному интерфейсу

Несколько периферийных устройств, подключенных к одному интерфейсу

Подключение к плате DataFlash

Подключение к плате DataFlash

Подключение к USB-плате CY7C68013A

Подключение к USB-плате CY7C68013A

Подключение к плате VGA PS2

Подключение к плате VGA PS2

Подключение к любой необходимой плате аксессуаров

Подключение к любой необходимой плате аксессуаров

Примечание:Open3S500E не интегрирует функции программирования/отладки, требуется программатор/отладчик.Дополнительные платы на фото не входят в стандарпосылка упаковку Open3S500E.

ПримерыМакетная плата Open3S500E FPGA поставляется с различными примерами кодов для поддерживаемых периферийных устройств, которые позволяют быстро начать разработку собственного приложения.

Периферийный Описание Интерфейс Маног VHDL AT24CXX EEPROM I2C Y Y FM24CXX Фрам I2C Y Y AT45DBXX DATAFLASH SPI Y PCF8563 RTC I2C Y PCF8591 4xAD, 1xDA I2C Y DS18B20 Датчик температуры 1-провод Y SP3232 Серийная связь UART Y Y SP3485 Серийная связь UART Y Y PL2303 USB для UART UART Y Y CY7C68013A Usb-устройство I/Os Y Зуммер Звуковое устройство 1I/O (PWM) Y Y Клавиатура PS/2 Входное устройство PS/2 Y Y Одиночные кнопки Входное устройство ---- Y Y 4x4 клавиатура Входное устройство 8I/Os Y Y Джойстик Входное устройство 5I/Os Y Y Светодиодный Устройство отображения ---- Y Y 8 seg светодиодный Устройство отображения 13I/Os Y Y Монитор VGA Устройство отображения VGA Y Y Символьный ЖК Устройство отображения 11I/Os Y Y Графический ЖК Устройство отображения 11I/Os Y Y Интерфейс отладки/программированияМакетная плата Open3S500E FPGA объединяет интерфейс JTAG для программирования/отладки.

Ресурсы для развития

Ресурсы для развития

Макетная плата Open3S500E FPGA поставляется с руководством пользователя CD, включая ресурсы разработки, перечисленные ниже:

Сопутствующее программное обеспечение (Xilinx ISE 12-Поддерживает Winxp/Win7, не поддерживает Win8) Демонстрационный код (каног, VHDL) Схема (PDF) Документации по разработке ПЛИС Посылка содержит

-

Debugging/Programmingsupports JTAG

-

Demo Board TypeOthers

-

FPGA pins expanderVCC, GND and all the I/O ports

-

I/Os116

-

JTAG interfacefor debugging/programming

-

Model NameOpen3S500E Standard

-

Open3S500Ean FPGA development board

-

Operating Frequency50MHz

-

Operating Voltage1.15V~3.3V

-

PackageQFP208

-

XC3S500Ethe XILINX Spartan-3E FPGA device

-

Вес логистики0.3

-

Каждая упаковка1

-

Минимальная единица измерения100000015

-

Название брендаWaveshare

-

Номер моделиOpen3S500E Standard

-

Продано Вsell_by_piece

-

Размер логистики - высота (см)10

-

Размер логистики - длина (см)20

-

Размер логистики - ширина (см)18

-

Тип демонстрационной доскиРука