Последнее обновление: 29.03.2022

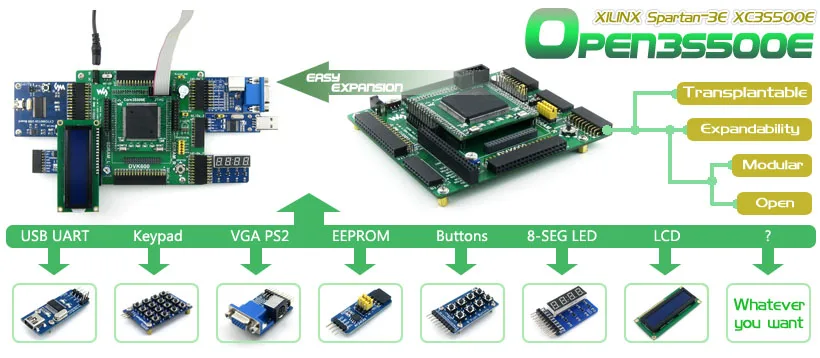

Xilinx FPGA развитию Xilinx Spartan-3E XC3S500E оценки комплект + DVK600 + XC3S500E Основные комплект = Open3S500E стандарт

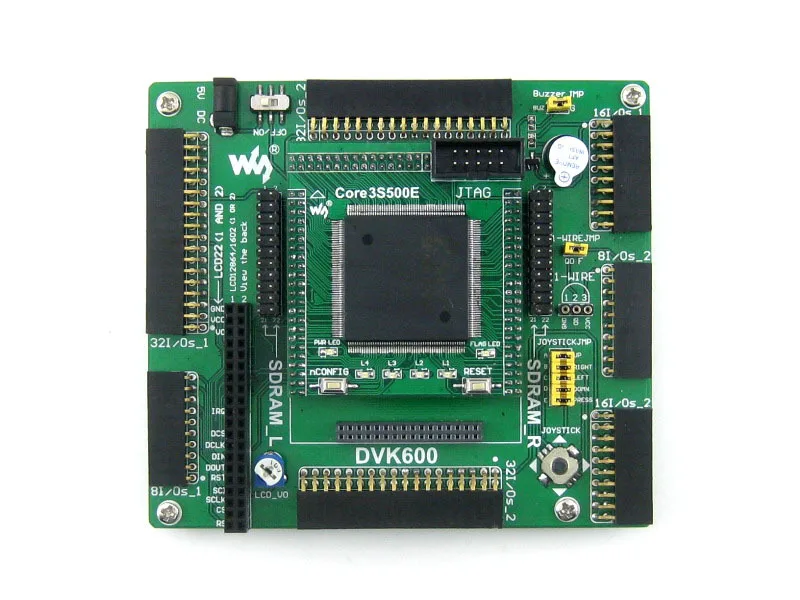

Open3S500E это FPGA развития совет, который состоит из материнской платы DVK600 и FPGA основной плате Core3S500E .

Open3S500E поддерживает дальнейшее расширение различных дополнительных плат аксессуар для конкретного приложения. Модульная и открытая конструкция делает его идеальным для начала разработки приложений с Xilinx Spartan-3E серии FPGA устройств.

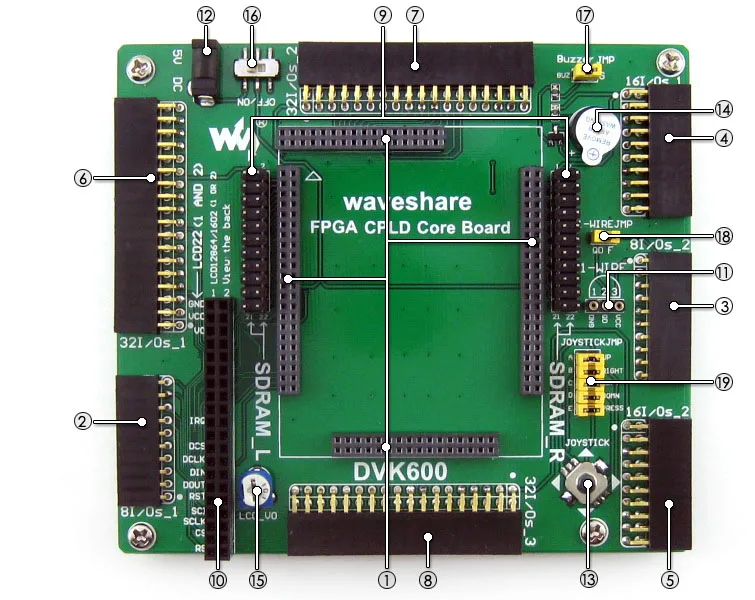

То, что на материнской плате

Все i/o интерфейсы выше:

Способен быть смоделированы как UART, I2C, SPI, PS/2, и др. Способный управлять устройств, таких как FRAM, вспышка, USB, Ethernet, и др.Для перемычки 17-19:

Короткий перемычки для подключения ввода/вывода, используемые в примере кода Откройте перемычки для подключения других пользовательских контактов с помощью перемычек, DVK600 поддерживает широкий спектр различных основной платы, Поэтому, Некоторые интерфейсов может быть не подключен и бесполезно при подключении к некоторым продуктам основной плате. Например, при подключении к Core3S500E/CoreEP2C8, '8. 32I/Os_3 "не подключен.

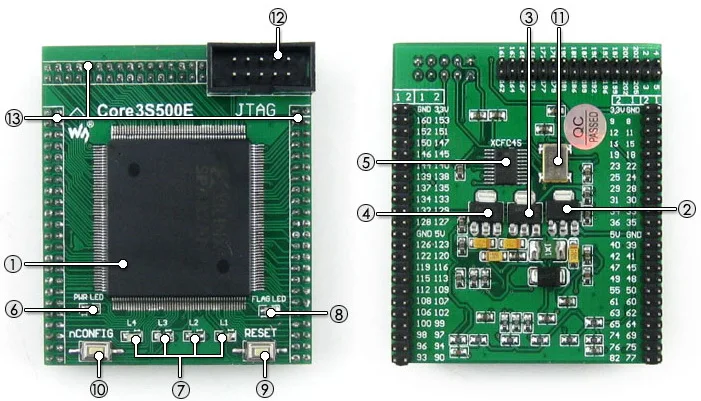

Что на Core3S500E

Open3S500E развитию

Open3S500E развитию  Open3S500E развитию

Open3S500E развитию  Open3S500E развитию вид сзади

Open3S500E развитию вид сзади  Материнской платы DVK600

Материнской платы DVK600  FPGA основной плате Core3S500E

FPGA основной плате Core3S500E  FPGA основной плате Core3S500E

FPGA основной плате Core3S500E  Подключение к LCD12864

Подключение к LCD12864  Подключение к LCD1602

Подключение к LCD1602  Подключение к порт RS232

Подключение к порт RS232  При подключении к USB-UART совета

При подключении к USB-UART совета  Подключение до 8 SEG светодиодные табло

Подключение до 8 SEG светодиодные табло  Подключение до 8 Кнопки

Подключение до 8 Кнопки  Подключения 4x4 клавиатуры

Подключения 4x4 клавиатуры  Подключение к EEPROM совета

Подключение к EEPROM совета  Мульти периферийные устройства подключен к Один интерфейс

Мульти периферийные устройства подключен к Один интерфейс  Подключение к DataFlash совета

Подключение к DataFlash совета  Подключение к USB совет CY7C68013A

Подключение к USB совет CY7C68013A  Подключение VGA PS2 доска

Подключение VGA PS2 доска  Подключение к любой аксессуар вам нужен совет

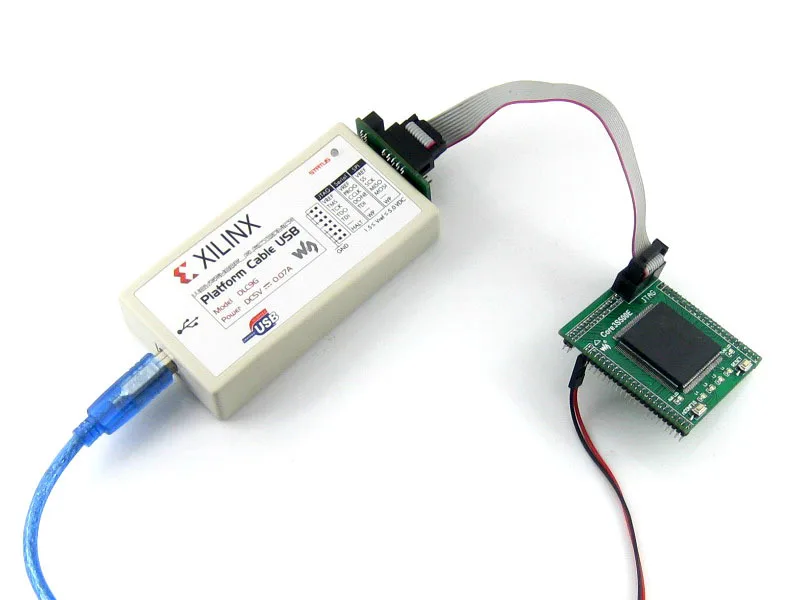

Подключение к любой аксессуар вам нужен совет Примечание: , Open3S500E НЕ интегрировать любые программирования/функции отладки, программатор/отладчик требуется. Аксессуары в фото не включены в Open3S500E стандартный пакет.

Примеры, Open3S500E FPGA развития плата поставляется с разнообразными примерами кодов для поддерживаемых периферийных устройств, Которые дают вам быстро приступить к разработке собственных приложений.

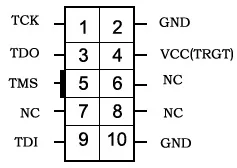

Периферической Описание Интерфейс Verilog VHDL AT24CXX EEPROM I2C Y Y FM24CXX FRAM I2C Y Y AT45DBXX DataFlash SPI Y PCF8563 RTC I2C Y PCF8591 4xAD, 1xDA I2C Y DS18B20 Датчик температуры 1-Wire Y SP3232 Последовательной связи UART Y Y SP3485 Последовательной связи UART Y Y PL2303 USB к UART UART Y Y CY7C68013A USB устройства Ввода/вывода Y Зуммер Звуковое устройство 1и/o-импульсной модуляции (PWM) Y Y PS/2 клавиатура Устройства ввода PS/2 Y Y Единой кнопки Устройства ввода ---- Y Y 4x4 клавиатуры Устройства ввода 8I/OS Y Y Джойстик Устройства ввода 5и/OS Y Y Светодиодные Устройства отображения ---- Y Y 8 SEG светодиодные Устройства отображения 13I/OS Y Y VGA монитор Устройства отображения VGA Y Y Характер ЖК- Устройства отображения 11I/OS Y Y Графический ЖК-дисплей Устройства отображения 11I/OS Y Y Отладка/Программирование интерфейса, Open3S500E FPGA развитию интегрирует JTAG интерфейс для программирования и отладки.

, Open3S500E FPGA развития плата поставляется с руководство пользователя CD, в том числе развития ресурсы, перечисленные ниже:

Соответствующее программное обеспечение (xilinx ISE 12- Поддерживает winxp/win7, не поддержка Win8 ) Демо-кода (Verilog, VHDL) Схемы (PDF) ПЛИС разработка документации Пакет содержит