Последнее обновление: 06.04.2022

5 шт./лот

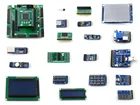

CoreEP4CE6-это основная плата FPGA, которая оснащена встроенным устройством EP4CE6E22C8N, поддерживает дальнейшее расширение.

Бортовое последовательное устройство конфигурации EPCS16SI8N

Интегрированная Базовая схема FPGA, такая как часы

Встроенная кнопка nCONFIG, кнопка сброса, 4 светодиода

Все порты ввода/вывода доступны на контактных заголовках

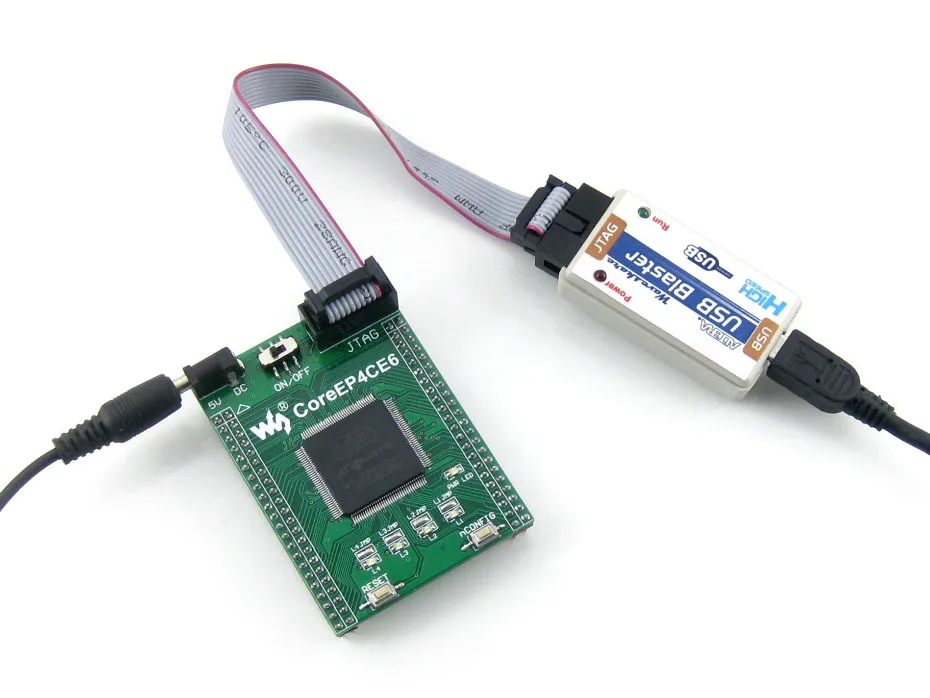

Бортовой JTAG отладка/программирование интерфейс

2,54 мм шаговый шаг, подходит для подключения к вашей системе приложений

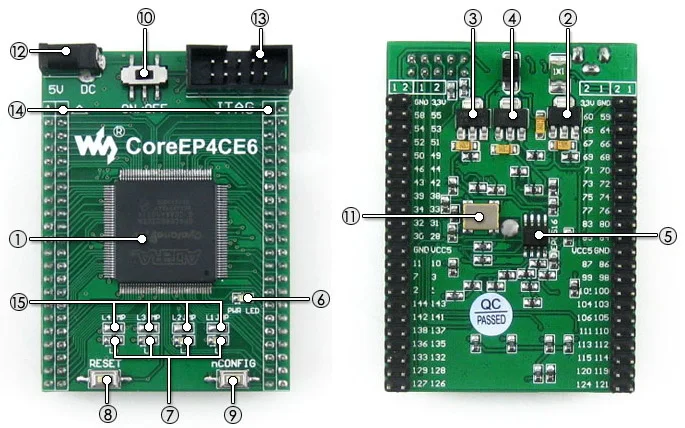

Что на борту

Рабочая частота: 50 МГц

Рабочее напряжение: 1,15 в ~ 3,465 в

Посылка: QFP144

I/Os: 80

LEs: 6K

RAM: 270кб

PLLs: 2

Отладка/программирование: Поддержка jtag

AMS1117-3.3, 3,3 V регулятор напряжения

AMS1117-2.5, 2,5 V регулятор напряжения

AMS1117-1.2, 1,2 V регулятор напряжения

EPCS16, Встроенная последовательная флэш-память, для хранения кода

Индикатор питания

Светодиоды

Кнопка сброса

Кнопка nCONFIG: Для повторной настройки чипа FPGA, эквивалент перезарядки питания

Выключатель питания

50 м активный кристаллический осциллятор

5V DC jack

Интерфейс JTAG: Для отладки/программирования

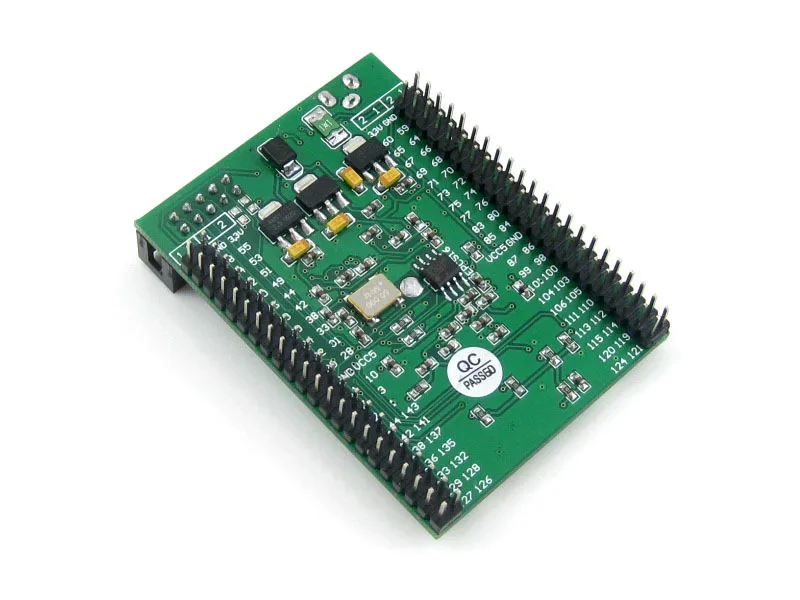

Расширитель FPGA pins, VCC, GND и все порты ввода/вывода доступны на разъемах расширения для дальнейшего расширения

Светодиодный джемпер

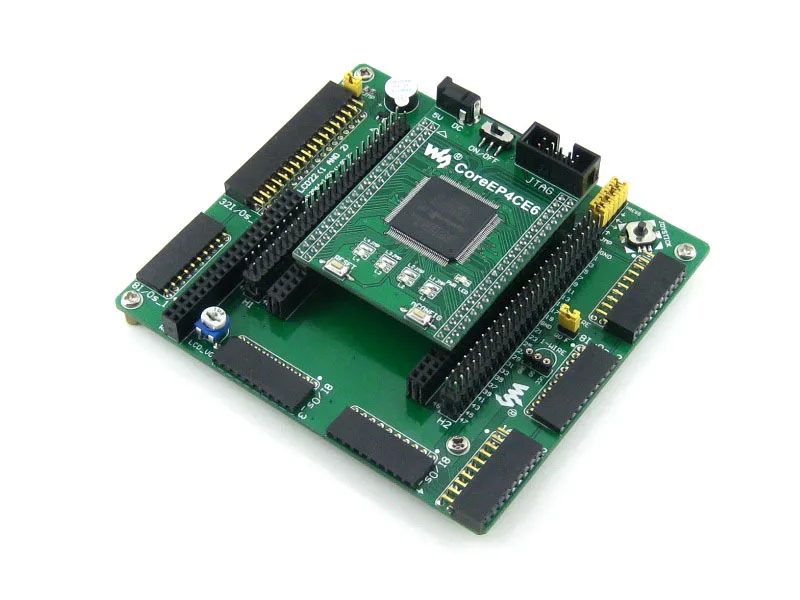

Фотографии

Примечание:CoreEP4CE6 предоставляет интерфейс отладки JTAG, но не интегрирует любую функцию отладки, требуется отладчик.Материнская плата и программист/отладчик на фотографиях не включены в цену.

Интерфейс JTAGНа рисунке ниже показана надпись JTAG

Сопутствующее программное обеспечение (Quaters II, NIOS II и т. Д.)

Демонстрационный код (Verilog, VHDL, NIOS II C)

Схема (PDF)

FPGA разработка документов

Вики: Www.waveshare.com/wiki/CoreEP4CE6

Вес: 0,074 кг

Основная плата CoreEP4CE6 x 5

Кабель питания USB x 5